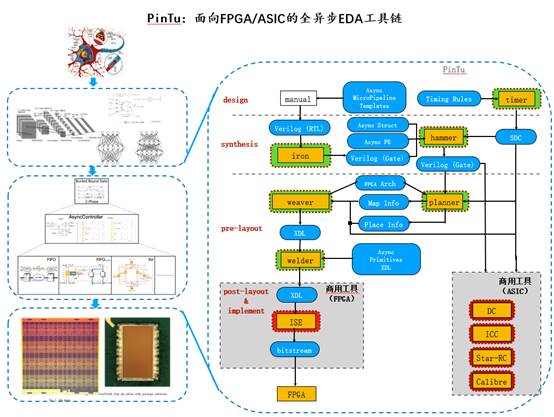

PinTu電子設計自動化(EDA)軟件,是國際上最早的面向BBD型自定時型異步電路的EDA工具鏈。此工具提供了豐富的異步微流水線模版和全異步算子模塊,使用者采用Verilog HDL并結合模版可設計出RTL級異步電路。此工具針對異步設計進行綜合、延遲匹配與時序驗證和仿真功能,完成從RTL級到門級工藝網表的綜合,提供面向FPGA的布圖和比特流生成功能,以及商用EDA的接口。

PinTu電子設計自動化(EDA)軟件,是國際上最早的面向BBD型自定時型異步電路的EDA工具鏈。此工具提供了豐富的異步微流水線模版和全異步算子模塊,使用者采用Verilog HDL并結合模版可設計出RTL級異步電路。此工具針對異步設計進行綜合、延遲匹配與時序驗證和仿真功能,完成從RTL級到門級工藝網表的綜合,提供面向FPGA的布圖和比特流生成功能,以及商用EDA的接口。

異步優勢及發展現狀

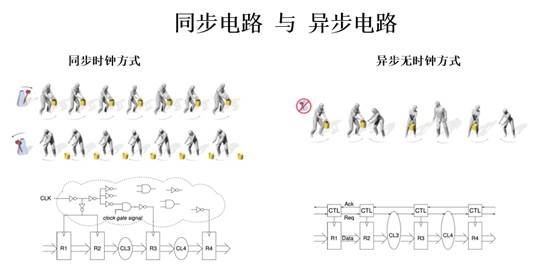

隨著半導體工藝的持續進步,同步電路由于全局時鐘導致的時鐘扭曲、時鐘功耗等問題日益突出,尤其在超大規模同步電路設計中瓶頸凸顯。而異步電路工作基于事件驅動,具有同步電路無法企及的低功耗、高可靠、高魯棒性、高可擴展性的特性,在物聯網、醫療、安全領域、惡劣環境高可靠性電路等方面具有廣泛的應用前景,得到國外知名企業及研究團隊的關注和投入,如曼徹斯特大學的SpiNNaker 、IBM 的TrueNorth、Intel的Loihi等芯片等。

異步電路采用局部通信模式,以握手協議完成異步控制,不需要龐大的時鐘分布網絡,避免了時鐘歪斜的問題,體現出模塊化強和電磁輻射低的優勢。除此之外,這種電路空閑時幾乎沒有消耗,散熱極低,整個系統的功耗得到有效控制。異步電路適合“大并發”形式的計算。但目前異步電路仍處于發展階段,國內外尤其缺乏面向最新的自定時型異步電路的專用設計自動化工具,嚴重制約了該領域的發展與應用。

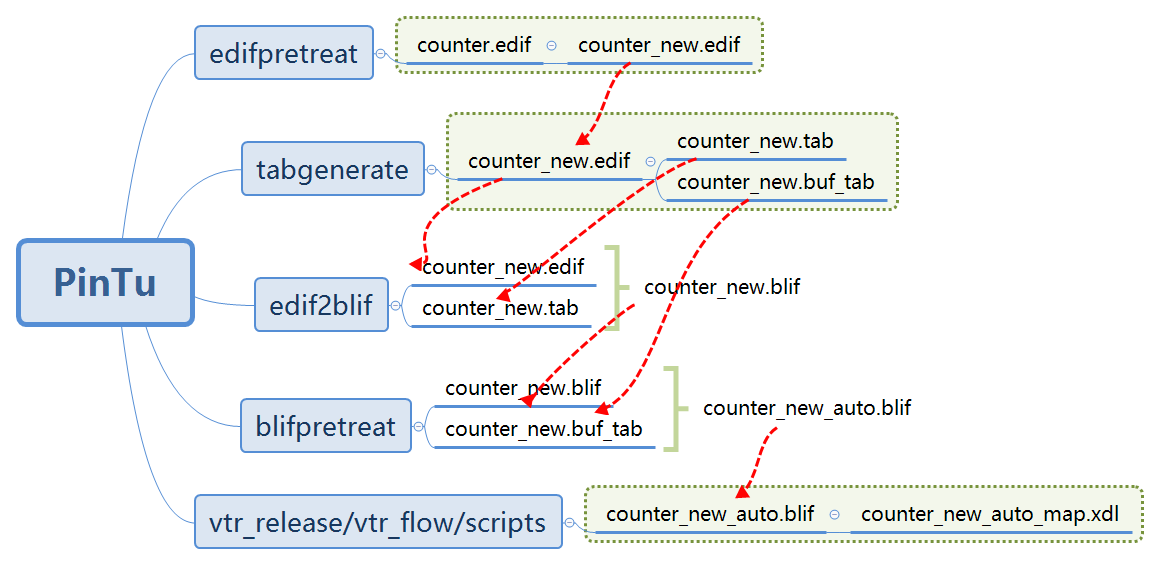

FPGA上PinTu操作流程

詳細操作流程參考代碼倉庫中的README.md